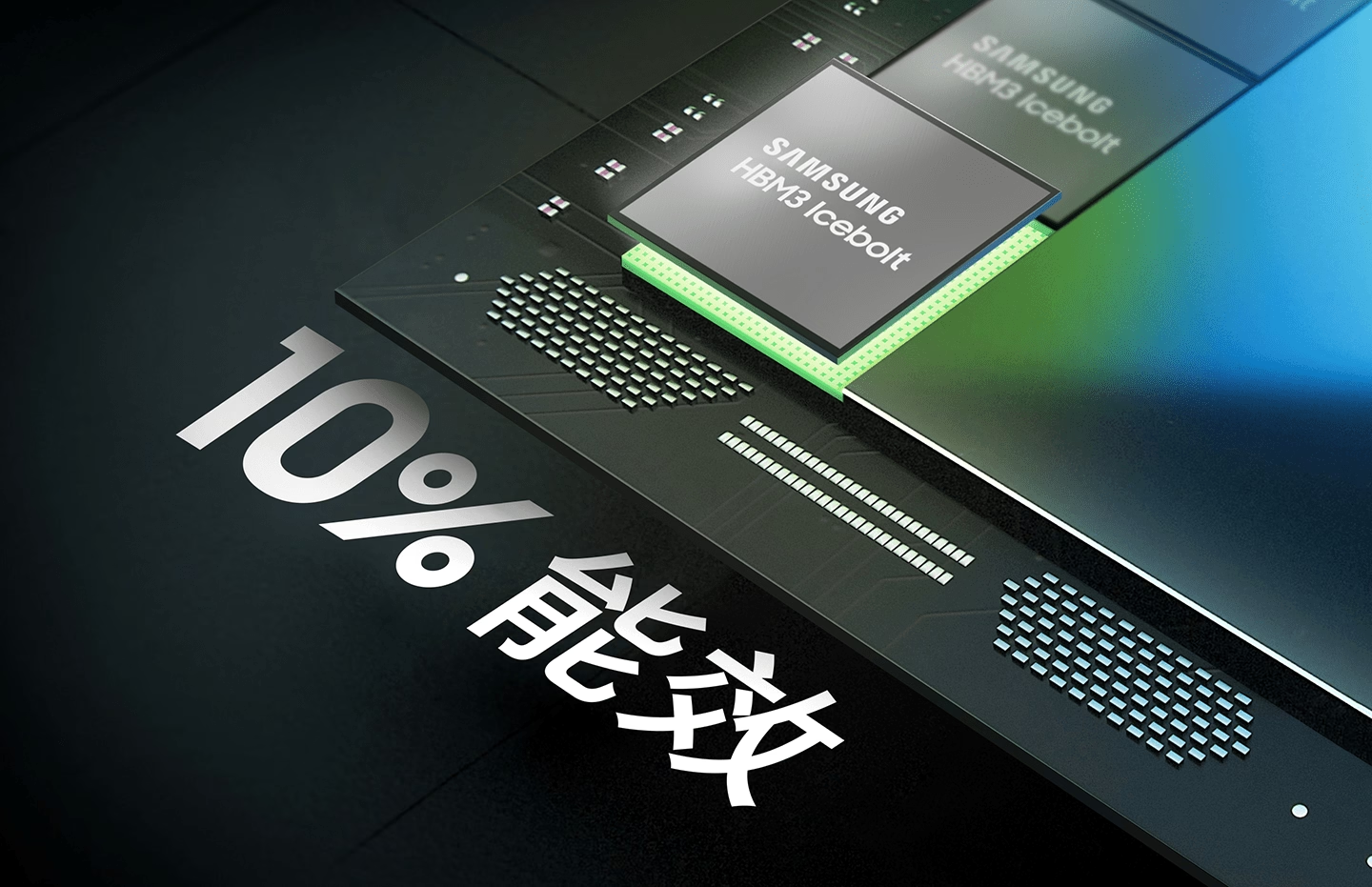

在Analyst Day 2024,Marvell(美满电子)宣布推出用于定制XPU的定制高带宽存储器(CHBM)解决方案,该XPU面向AI应用。该方案是与领先的内存制造商合作开发的,CHBM承诺为特定的XPU设计优化性能、功耗、内存容量、芯片尺寸和成本。CHBM将与Marvell的定制XPU兼容,并且至少在初期不会成为JEDEC定义的HBM标准的一部分。

Marvell的定制HBM解决方案允许为特定应用定制接口和堆栈,尽管公司尚未透露任何细节。Marvell的目标之一是减少行业标准HBM接口在处理器内部所占用的空间,从而释放可用于计算和功能的区域。公司声称,凭借其专有的芯片间I/O,它不仅能够在其定制XPU中多封装25%的逻辑,还可能在与计算Chiplet相邻的地方多安装33%的CHBM内存封装,从而增加处理器可用的DRAM量。此外,公司预计内存接口功耗将降低高达70%。

由于Marvell的CHBM不依赖于JEDEC指定的标准,因此在硬件方面,它将需要一个新控制器和可定制的物理接口、新的芯片间接口以及彻底改造的HBM基础芯片。新的Marvell芯片间HBM接口带宽为20Tbps/mm(2.5TB/s每毫米),这比目前HBM提供的5Tbps/mm(625GB/s每毫米)有显著提升。随着时间的推移,Marvell设想无缓冲内存的带宽将达到50Tbps/mm(6.25TB/s每毫米)。

Marvell没有具体说明其CHBM接口的宽度。除了表示其“通过串行化和加速其内部AI计算加速器硅芯片与HBM基础芯片之间的I/O接口来增强XPU”外,Marvell没有透露其定制HBM解决方案的许多细节,这某种程度上暗示了与行业标准HBM3E或HBM4解决方案相比,接口宽度较窄。然而,看起来CHBM解决方案将是可定制的。

“通过为特定性能、功耗和总体拥有成本定制HBM来增强XPU,是AI加速器设计和交付新范式中的最新一步,”Marvell定制、计算和存储组高级副总裁兼总经理Will Chu表示。“我们非常感谢与领先的内存设计商合作,以加速这场革命,并帮助云数据中心运营商继续扩展其XPU和基础设施,以迎接AI时代。”

与美光、三星和SK海力士的合作对于Marvell CHBM的成功实施至关重要,因为这为定制HBM的相对广泛利用奠定了基础。(校对/赵月)